Soliton 數位協定自動化驗證方案 - I3C

Soliton Technologies 是一家專注於數位協定驗證解決方案的公司,特別是在 MIPI I3C® 協定方面。其 I3C Protocol Validation Suite 利用 NI 的 PXI 平台 ( PXIe-6570 / 6571 ),提供自動化的功能、時序和電氣符合性測試,涵蓋 SDR、HDR-DDR 模式、動態位址分配、In-Band Interrupts 等功能,並支援錯誤注入與容錯測試,協助半導體公司快速驗證產品的協定相容性。

Soliton 數位協定驗證方案

-

Device Read/Write

-

Interrupts

-

Device Addressing, etc.

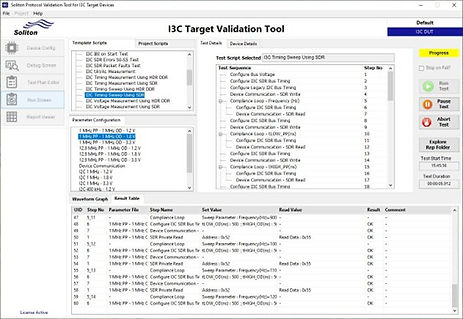

Soliton 數位協定驗證方案軟體介面

I3C 協定簡介

-

MIPI I3C® 是一種可擴展的中速公用與控制匯流排,廣泛用於手機、穿戴式裝置與汽車電子

-

目標在於簡化周邊元件與應用處理器的連接,提升整合效率並降低成本。

驗證挑戰

-

隨協定與產品設計日益複雜,傳統手動驗證方法耗時費力,延後產品上市時程。

-

確保協定相容性與異常狀況容錯能力成為驗證關鍵。

Soliton I3C Validation Suite 優勢

-

基於 NI PXI 平台,提供自動化、即插即用的驗證工具。

-

支援時序與電氣規範驗證,並可測試容錯與異常回復能力。

-

自動產生完整測試報告,提升除錯與驗證效率。

-

用戶經驗顯示,可將驗證時間從數週縮短至數天。

Soliton I3C Validation Suite 組成

Soliton 的 I3C Validation Suite 是一套現成的驗證工具,搭載 NI PXI 平台,協助驗證裝置是否符合 MIPI I3C® 協定的時序與電氣規格。其組成包含以下元件:

-

NI PXIe 657x ─ 數位模式產生卡,搭配 PXIe 機箱架構

-

Soliton PVS 轉接板(Interposer Board)

-

示波器 ─ 執行電壓量測

-

Soliton I3C Validation Suite 軟體 ─ 支援 Windows 作業系統 (Windows 10)

MIPI I3C Protocal - Functional Coverage

-

I3C SDR Mode (15 MHz)

-

I3C HDR-DDR Mode (15 MHz)

-

Legacy I2C Mode (5 MHz)

-

Register Write (Legacy I2C/SDR/HDR)

-

Register Read (Legacy I2C/SDR/HDR)

-

Write N Bytes (Legacy I2C/SDR/HDR)

-

Read N Bytes (Legacy I2C/SDR/HDR)

-

Write N - Read N Bytes (Combined Format) (Legacy I2C/SDR/HDR)

-

Hot Join Funtional Test

-

IBI Funtional Test

-

IBI Interrupt Spacing Test

-

Clock Stalling

-

SDR and HDR DDR CCC Commands

-

Compliance Test Suite (CTS)

-

Dynamic/Statics Addressing

-

Direct and Broadcast CCC Commands

-

Start / Stop Coditions

-

Address Header and Transition Bit

-

HDR DDR Restart and Exit Patterns

-

Target Reset Patterns

-

Group Target Addressing

-

Induce SDR Errors (S0-S5)

-

Induce HDR / DDR Errors

-

Skip Start / Stop / Repeated Start

-

Skip HDR Restarts / HDR Exit

-

Add Clock from Address / data bytes

-

Skip Clock from Address / data bytes

-

Induce Parity / Preamble Errors

-

Induce Error in CRCS Calculation

-

Any Custom Faults in SDR / HDR DRR Transactions and can Check if the Slave is able to Recover from the Faults

MIPI I3C Protocal - Parametric Coverage

-

fSCL - SCL Clock Frequency

-

tSU - STA - Setup Time for Repeated Start

-

tHD - STA - Hold Time for a (Repeated ) Start

-

tLow, tDIG_L - SCL Clock Low Period

-

tHIGH, tDIG_H - SCL Clock High Period

-

tSU - DAT - Data Setup Time

-

tHD - DAT - Data Hold Time

-

trCL - SCL Single Rise Time

-

tfCL - SCL Single Fall Time

-

trDA - SDA Single Rise Time

-

tfDA - SDA Single Fall Time

-

tSU_STO - Setup Time for Stop

-

tBUF - Bus Free Time Between a Stop and a Start

-

tSPIKE - Pluse Width of Spikes to Supress

-

tLOW_OD, tDIG_OD_L-Low Period of SCL Clock

-

tHIGH_OD, tDIG_OD_H-High Period of SCL Clock

-

tfDA_OD - Fall Time of SDA Signal

-

tSU_OD - Data Setup Time During Open - Drain Mode

-

tCAS - Clock after Start Condition

-

tCBP - Clock before Stop Condition

-

tAVAL - Bus Available Condition

-

tIDLE - Bud Idle Condition

-

fSCL - SCL Clock Frequency

-

tLOW_PP, tDIG_L - SCL Clock Low Period

-

tHIGH_PP, tDIG_H - SCL Clock High Period

-

tSCO - Clock in to Data out for Slave

-

tCR - SCL Clocl Rise Time

-

tCF - SCL Clocl Fall Time

-

tHD_PP - SDA Signal Data Hold in Push - Pull Mode

-

tSU_PP - SDA Signal Data Setup in Push - Pull Mode

-

tCASr - Clock after Repteated Start Condition

-

tCBSr - Clock before Repteated Start Condition

-

VIL - Low-Level Input Voltage

-

VIH - High-Level Input Voltage

-

Vhys - Schmitt Trigger Input Hysteresis

-

VOL - Output Low Level

-

VOH - Output High Level